Kirim:info@anke-pcb.com

Whatapp / Wechat: 008618589033832

Skype: SannyDuNbsp

Telung aspek kanggo ngamanake integritas daya ingDesain PCB

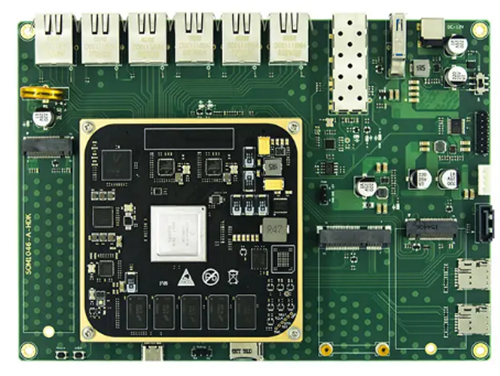

Ing desain elektronik modern, integritas daya minangka bagean desain PCB sing penting banget. Kanggo njamin operasi stabil lan kinerja piranti elektronik, kita kudu nimbang lan desain kanthi lengkap saka sumber daya menyang panrima.

Liwat kanthi ati-ati ngrancang lan ngoptimalake modul daya, pesawat lapisan jero, lan kripik listrik bisa kita entuk integritas tenaga. Artikel iki uga bakal bisa ngerteni telung aspek penting kanggo nyedhiyakake tuntunan lan strategi praktis kanggo desainer PCB.

I. Kabel Modul Power

Modul daya minangka sumber energi saben piranti elektronik, kinerja lan tata letak langsung mengaruhi stabilitas lan efisiensi sistem kabeh. Tata letak lan rute sing bener ora mung bisa nyuda gangguan swara nanging uga njamin aliran saiki, saéngga ningkatake kinerja sakabèhé.

Tata letak modul 2.POWER

1.Sawise pangolahan:

Modul daya kudu dibayar khusus amarga dadi titik wiwitan kekuwatan. Kanggo nyuda introduksi swara, lingkungan sekitar modul daya kudu dijaga kanthi resik kanggo ngindhari jarak liyanefrekuensi tinggiutawa komponen sensitif swara.

2.Culung menyang chip pasokan listrik:

Modul Daya kudu diselehake minangka cedhak karo chip sing diwenehake. Iki bisa nyuda kerugian ing proses transmisi saiki lan nyuda syarat-syarat pesawat lapisan jero.

3.Sawise dissipasi:

Modul Daya bisa ngasilake panas sajrone operasi, saengga kudu dipesthekake yen ora ana alangan ing ndhuwur kanggo dissipasi panas. Yen perlu, heatsinks utawa penggemar bisa ditambah kanggo pendinginan.

4.Amoiding puteran:

Nalika rute, supaya mbentuk gelung saiki kanggo nyuda kemungkinan gangguan elektromagnetik.

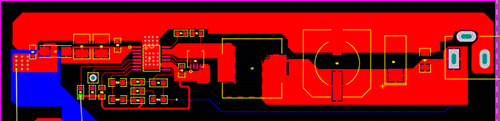

II. Perencanaan Desain Plane Lapisan Lapisan

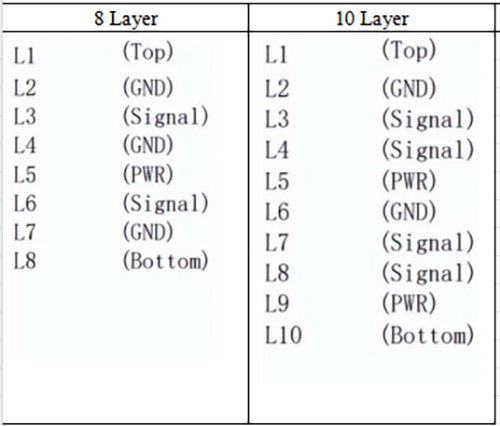

A. Desain tumpukan lapisan

In Desain PCB EMC, Desain tumpukan lapisan minangka unsur utama sing kudu nimbang distribusi rute lan daya.

a. Kanggo njamin karakteristik impedance sing kurang saka pesawat listrik lan nyerep ground ground, jarak antara pesawat lan lemah ora bisa ngluwihi 10mil, biasane disaranake kurang saka 5mil.

b. Yen pesawat daya siji ora bisa ditindakake, lapisan permukaan bisa digunakake kanggo nglebokake pesawat listrik. Plaring lemah sing cedhak lan lemah mbentuk pesawat kapasitor pesawat kanthi impedansi AC minimal lan karakteristik frekuensi sing dhuwur banget.

c. Ngindhari rong lapisan tenaga, utamane kanthi beda voltase gedhe, kanggo nyegah coupling swara. Yen ora bisa diendhani, nambah jarak ing antarane rong lapisan tenaga sabisa.

d. Ples Referensi, utamane pesawat referensi daya, kudu njaga ciri khas impedance sing sithik lan bisa dioptimalake liwat kapasitor bypass lan lapisan lapisan.

Segmen daya b.multiple

a. Kanggo sumber daya cilik cilik, kayata voltase kerja inti saka chip ic tartamtu, tembaga kudu dilebokake ing lapisan sinyal kanggo njamin integritas daya listrik ing lapisan lumahing kanggo nyuda radiasi permukaan.

b. Pilihan ambane segmen kudu cocog. Nalika voltase luwih saka 12V, jembaré bisa 20-30mil; Yen ora, pilih 12-20mil. Lebar segmen antarane Sumber Daya Analog lan Digital kudu ditambah kanggo nyegah kekuwatan digital ora campur tangan karo kekuwatan analog.

c. Jaringan tenaga prasaja kudu rampung ing lapisan rute, lan jaringan listrik luwih akeh kudu kaparing kaparing sing ditambahake.

d. Pesawat Daya Segmen kudu tetep rutin supaya ora duwe bencana nyebabake résonansi lan impedansi daya tambah. Strip sing dawa lan sempit lan divisi berbentuk dumbbell ora diidini.

C.Plane Filter

a. Pesawat listrik kudu digandhengake karo pesawat lemah.

b. Kanggo Kripik kanthi frekuensi operasi ngluwihi 500mhz, utamane gumantung karo panyaring pesawat lan nggunakake kombinasi panyaring capacitor. Efek nyaring kudu dikonfirmasi kanthi simulasi integritas daya.

c. Instal induktor kanggo kapasitor decoupling ing pesawat kontrol, kayata widening kapasitor nyebabake lan nambah kapasitor liwat, kanggo mesthekake yen impedansi daya lemah luwih murah tinimbang impedans target.

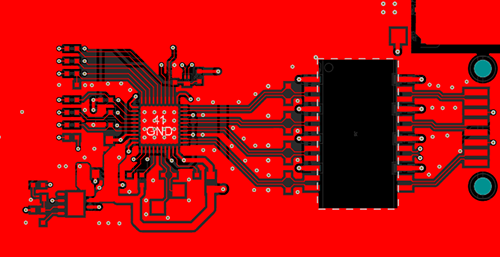

III. Tata letak chip Power

Chip daya minangka inti piranti elektronik, lan mesthekake integritas kekuwatan penting kanggo ningkatake kinerja piranti lan stabilitas. Kontrol integritas daya kanggo Kripik Daya utamane kalebu rocking penanganan listrik chip lan tata letak lan wiring kapasain sing bener. Ing ngisor iki bakal menehi saran rinci lan saran praktis babagan aspek kasebut.

Rute Pin Pom PIN

Rute pin pins chip minangka bagian saka kontrol integritas daya. Kanggo nyedhiyakake pasokan saiki, dianjurake kanggo nglukis pin tenaga pins, umume padha karo chip chip. Biasane, ingjembar minimalora kurang saka 8mil, nanging asil sing luwih apik, coba entuk ambane 10mil. Kanthi nambah ambane rute, impedan bisa dikurangi, saengga bisa nyuda daya lan njamin persediaan sing cukup kanggo chip.

B.Layout lan rute kapasitor decoupling

Kapasitor decoupling duwe peran penting kanggo kontrol integritas daya kanggo Kripik Daya. Gumantung ing ciri capacitor lan syarat aplikasi, kapasitor sing dihiasi umume dipérang dadi kapasitor cilik.

a. Kapasis gedhe: Kapasis gedhe biasane disebar ing sekitar chip. Amarga frekuensi resonant ngisor lan radius nyaring kanthi luwih gedhe, bisa nyaring swara frekuensi kanthi efektif lan nyedhiyani sumber daya stabil.

b. Kapasitor cilik: Kapalit cilik duwe frekuensi resonant sing luwih dhuwur lan radius panyaring sing luwih cilik, saengga kudu dipasang cedhak karo chip pin. Nyelehake adoh banget bisa uga ora nyaring swara swara sing dhuwur banget, ilang efek dekupling. Tata letak sing bener mesthekake yen efektifitas kapasitor cilik ing nyaring swara frekuensi dhuwur kanthi lengkap.

C.Wiring metode kapasitas decoupling paralel

Kanggo nambah integritas daya, kapasitas sing asring degel asring disambungake ing podo. Tujuan utama praktik iki yaiku nyuda induktian seri (ESL) kapasitor individu liwat sambungan paralel.

Nalika podo karo pirang-pirang kapasti decoupling, perhatian kudu dibayar kanggo penempatan vaasi kanggo kapasitor. Praktek umum yaiku ngimbangi virus saka kekuwatan lan lemah. Tujuan utama iki yaiku nyuda induktif bebarengan ing antarane kapasitor sing dihiasi. Mesthekake yen ora sopan luwih cilik tinimbang ESL kapasitor siji, saengga impedance ESL sakabehe sawise podo karo pirang-pirang kapasitas decoupling yaiku 1 / n. Kanthi nyuda induktif bebarengan, efisiensi nyaring bisa ditambah kanthi efektif, mesthekake stabilitas daya sing luwih apik.

Tata letakLan rute modul tenaga dhewe, Perencanaan Plancongan Plane Planage, lan nangani chip chip tenaga lan wiring sing penting banget lan wiring ora pati penting ing desain piranti elektronik. Liwat tata letak lan rute sing tepat, kita bisa njamin stabilitas lan efisiensi modul tenaga, nyuda gangguan swara, lan nambah kinerja sakabèhé. Desain tumpukan lapisan lan macem-macem segmen daya luwih ngoptimalake karakteristik pesawat, nyuda gangguan swara. Nangani chip chip chip lan kabel lan kapasitas sing tepat lan concitor integritas daya, mesthekake pasokan saiki sing stabil lan panyaring swara sing efektif, nerbitake kinerja piranti lan stabilitas.

Ing makarya praktis, macem-macem faktor kayata gedhene saiki, jembaré rute, nomer liwat, efek supling, lan sapiturute, kudu dianggep nggawe tata letak sing rasional lan keputusan sing rasional. Tindakake spesifikasi desain lan praktik paling apik kanggo njamin ngontrol lan optimasi integritas daya. Mung kanthi cara iki, kita bisa nyedhiyakake sumber daya stabil lan efisien kanggo piranti elektronik, ketemu tuntutan kinerja, lan nyopir pembangunan lan kemajuan teknologi elektronik.

Shenzhen Anke Pcb Co, Ltd

Wektu Pos: Mar-25-2024